- 您现在的位置:买卖IC网 > Sheet目录1214 > EVAL-ADE7880EBZ (Analog Devices Inc)BOARD EVAL FOR ADE7880

�� �

�

�

�Data� Sheet�

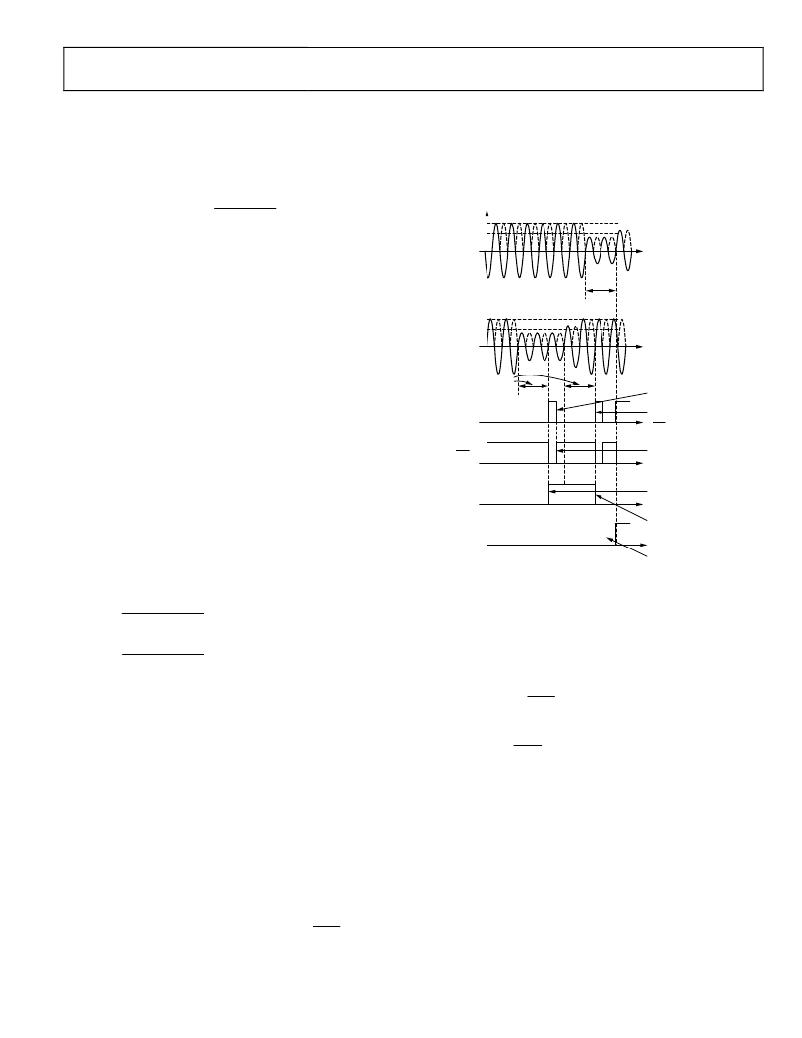

�256� kHz)� for� 60� Hz� systems.� The� delays� between� phase� voltages�

�or� phase� currents� are� used� to� characterize� how� balanced� the�

�load� is.� The� delays� between� phase� voltages� and� currents� are�

�used� to� compute� the� power� factor� on� each� phase� as� shown� in�

�the� following� Equation� 6:�

�ADE7880�

�in� STATUS1� register� is� set� to� 1� to� indicate� the� condition� and� the� bit�

�VSPHASE[0]� in� the� PHSTATUS� register� is� set� back� to� 0.�

�Bits� VSPHASE[1]� and� VSPHASE[2]� relate� to� the� sag� events� on�

�Phase� B� and� Phase� C� in� the� same� way:� when� Phase� B� or� Phase� C�

�voltage� stays� below� SAGLVL,� they� are� set� to� 1.� When� the� phase�

�360� o� � f� LINE� ?�

�?�

�cos� φ� x� =� cos� ?� ANGLEx� ×�

�?�

�?�

�256� kHz� ?�

�(6)�

�voltages� are� above� SAGLVL,� they� are� set� to� 0.�

�PHASE� B� VOLTAGE�

�FULL� SCALE�

�SAGLVL[23:0]�

�where� f� LINE� =� 50� Hz� or� 60� Hz.�

�Period� Measurement�

�The� ADE7880� provides� the� period� measurement� of� the� line� in�

�the� voltage� channel.� The� period� of� each� phase� voltage� is�

�measured� and� stored� in� three� different� registers,� APERIOD,�

�BPERIOD,� and� CPERIOD.� The� period� registers� are� 16-bit�

�unsigned� registers� and� update� every� line� period.� Because� of� the�

�LPF1� filter� (see� Figure� 50),� a� settling� time� of� 30� ms� to� 40� ms� is�

�SAGCYC[7:0]� =� 0x4�

�PHASE� A� VOLTAGE�

�associated� with� this� filter� before� the� measurement� is� stable.�

�The� period� measurement� has� a� resolution� of� 3.90625� μs/LSB�

�(256� kHz� clock),� which� represents� 0.0195%� (50� Hz/256� kHz)�

�when� the� line� frequency� is� 50� Hz� and� 0.0234%� (60� Hz/256� kHz)�

�when� the� line� frequency� is� 60� Hz.� The� value� of� the� period� registers�

�for� 50� Hz� networks� is� approximately� 5120� (256� kHz/50� Hz)� and�

�for� 60� Hz� networks� is� approximately� 4267� (256� kHz/60� Hz).� The�

�length� of� the� registers� enables� the� measurement� of� line� frequencies�

�as� low� as� 3.9� Hz� (256� kHz/2� 16� ).� The� period� registers� are� stable� at�

�±1� LSB� when� the� line� is� established� and� the� measurement� does�

�not� change.�

�The� following� equations� can� be� used� to� compute� the� line� period�

�and� frequency� using� the� period� registers:�

�SAGCYC[7:0]� =� 0x4�

�BIT� 16� (SAG)� IN�

�STATUS1[31:0]�

�IRQ1� PIN�

�VSPHASE[0]� =�

�PHSTATUS[12]�

�VSPHASE[1]� =�

�PHSTATUS[13]�

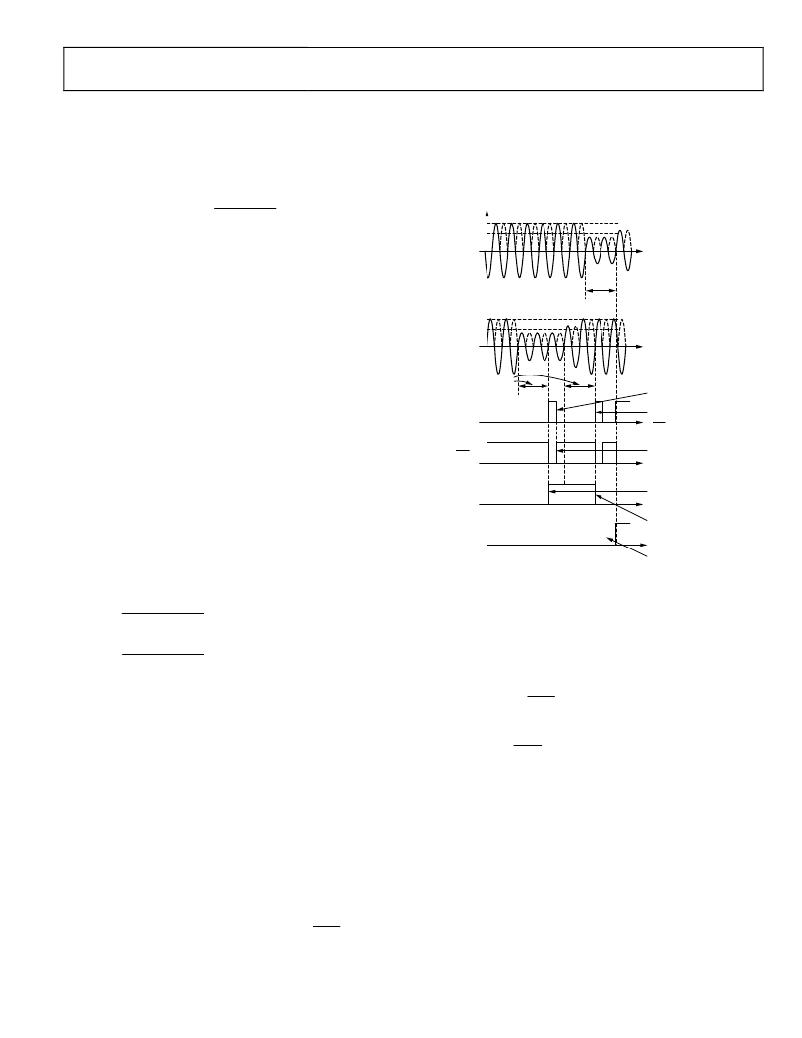

�Figure� 56.� SAG� Detection�

�STATUS1[16]� CANCELLED� BY�

�A� WRITE� TO� STATUS1[31:0]�

�WITH� SAG� BIT� SET�

�STATUS[16]� SET� TO� 1�

�IRQ1� PIN� GOES� HIGH�

�BECAUSE� STATUS1[16]�

�CANCELLED� BY� A� WRITE�

�TO� STATUS[31:0]� WITH� SAG�

�BIT� SET�

�PHSTATUS[12]� SET� TO� 1�

�BECAUSE� PHASE� A�

�VOLTAGE� WAS� BELOW�

�SAGLVL� FOR� SAGCYC�

�HALF� LINE� CYCLES�

�PHSTATUS[12]� CLEARED�

�TO� 0� BECAUSE� PHASE� A�

�VOLTAGE� WAS� ABOVE�

�SAGLVL� FOR� SAGCYC�

�HALF� LINE� CYCLES�

�PHSTATUS[13]� SET� TO� 1�

�T� L� =�

�f� L� =�

�PERIOD[15:0]�

�256� E� 3�

�256� E� 3�

�PERIOD[15� :0]�

�[� sec� ]�

�[� Hz� ]�

�(7)�

�(8)�

�The� SAGCYC� register� represents� the� number� of� half-line� cycles�

�the� phase� voltage� must� remain� below� or� above� the� level� indicated�

�in� the� SAGLVL� register� to� trigger� a� SAG� interrupt� ;� 0� is� not� a�

�valid� number� for� SAGCYC.� For� example,� when� the� SAG� cycle�

�(SAGCYC[7:0])� contains� 0x07,� the� SAG� flag� in� the� STATUS1�

�register� is� set� at� the� end� of� the� seventh� half� line� cycle� for� which�

�Phase� Voltage� Sag� Detection�

�The� ADE7880� can� be� programmed� to� detect� when� the� absolute�

�value� of� any� phase� voltage� drops� below� or� grows� above� a� certain�

�peak� value� for� a� number� of� half-line� cycles.� The� phase� where�

�this� event� takes� place� and� the� state� of� the� phase� voltage� relative�

�to� the� threshold� is� identified� in� Bits[14:12]� (VSPHASE[x])� of�

�the� PHSTATUS� register.� An� associated� interrupt� is� triggered�

�when� any� phase� drops� below� or� grows� above� a� threshold.� This�

���is� set� in� the� SAG� level� register� (SAGLVL)� for� four� half-line� cycles�

�(SAGCYC� =� 4).� When� Bit� 16� (SAG)� in� the� STATUS1� register� is� set�

�to� 1� to� indicate� the� condition,� Bit� VSPHASE[0]� in� the� PHSTATUS�

�register� is� also� set� to� 1� because� the� phase� A� voltage� is� below�

�SAGLVL.� The� microcontroller� then� writes� back� STATUS1� register�

�with� Bit� 16� (SAG)� set� to� 1� to� erase� the� bit� and� bring� IRQ1� interrupt�

�pin� back� high.� Then� the� phase� A� voltage� stays� above� the� SAGLVL�

�threshold� for� four� half-line� cycles� (SAGCYC� =� 4).� The� Bit� 16� (SAG)�

�the� line� voltage� falls� below� the� threshold.� If� Bit� 16� (SAG)� in�

�MASK1� is� set,� the� IRQ1� interrupt� pin� is� driven� low� in� case� of� a�

�SAG� event� in� the� same� moment� the� Status� Bit� 16� (SAG)� in�

�STATUS1� register� is� set� to� 1.� The� SAG� status� bit� in� the� STATUS1�

�register� and� the� IRQ1� pin� is� returned� to� high� by� writing� to� the�

�STATUS1� register� with� the� status� bit� set� to� 1.�

�When� the� Phase� B� voltage� falls� below� the� indicated� threshold�

�into� the� SAGLVL� register� for� two� line� cycles,� Bit� VSPHASE[1]�

�in� the� PHSTATUS� register� is� set� to� 1� (see� Figure� 56).� Simultane-�

�ously,� Bit� 16� (SAG)� in� the� STATUS1� register� is� set� to� 1� to� indicate�

�the� condition.�

�Note� that� the� internal� zero-crossing� counter� is� always� active.� By�

�setting� the� SAGLVL� register,� the� first� SAG� detection� result� is,�

�therefore,� not� executed� across� a� full� SAGCYC� period.� Writing� to�

�the� SAGCYC� register� when� the� SAGLVL� register� is� already� initia-�

�lized� resets� the� zero-crossing� counter,� thus� ensuring� that� the� first�

�SAG� detection� result� is� obtained� across� a� full� SAGCYC� period.�

�Rev.� A� |� Page� 33� of� 104�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

EVAL-ADE7953EBZ

BOARD EVAL FOR ADE7953

EVAL-ADF4002EBZ1

BOARD EVAL FOR ADF4002

EVAL-ADG788EBZ

BOARD EVALUATION FOR ADG788

EVAL-ADM1021AEB

BOARD EVAL FOR ADM1021

EVAL-ADM1023EB

BOARD EVAL FOR ADM1023

EVAL-ADM1031EB

BOARD EVAL FOR ADM1031

EVAL-ADM1062TQEBZ

BOARD EVALUATION FOR ADM1062TQ

EVAL-ADM1075CEBZ

BOARD EVAL FOR ADM1075

相关代理商/技术参数

EVAL-ADE7880EBZ

制造商:Analog Devices 功能描述:ADE7880, ENERGY METER, 3 PH, SPI, I2C, E

EVAL-ADE7913EBZ

制造商:AD 制造商全称:Analog Devices 功能描述:3-Channel, Isolated, Sigma-Delta ADC with SPI

EVAL-ADE7953EBZ

功能描述:BOARD EVAL FOR ADE7953 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源

EVAL-ADF4001EBZ2

制造商:Analog Devices 功能描述:Evaluation Board For Pll Frequency Synthesizer 制造商:Analog Devices 功能描述:ADF4001 PLL SYNTHESIZER EVAL BOARD

EVAL-ADF4002EB1

制造商:Analog Devices 功能描述:EVAL BOARD - Bulk

EVAL-ADF4002EBZ1

功能描述:BOARD EVAL FOR ADF4002 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 产品培训模块:Obsolescence Mitigation Program 标准包装:1 系列:- 主要目的:电源管理,电池充电器 嵌入式:否 已用 IC / 零件:MAX8903A 主要属性:1 芯锂离子电池 次要属性:状态 LED 已供物品:板

EVAL-ADF4007EBZ1

功能描述:BOARD EVALUATION FOR ADF4007EB1 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源

EVAL-ADF4106EB1

制造商:Analog Devices 功能描述:PLL, Frequency Synthesizer